# **Under Construction**

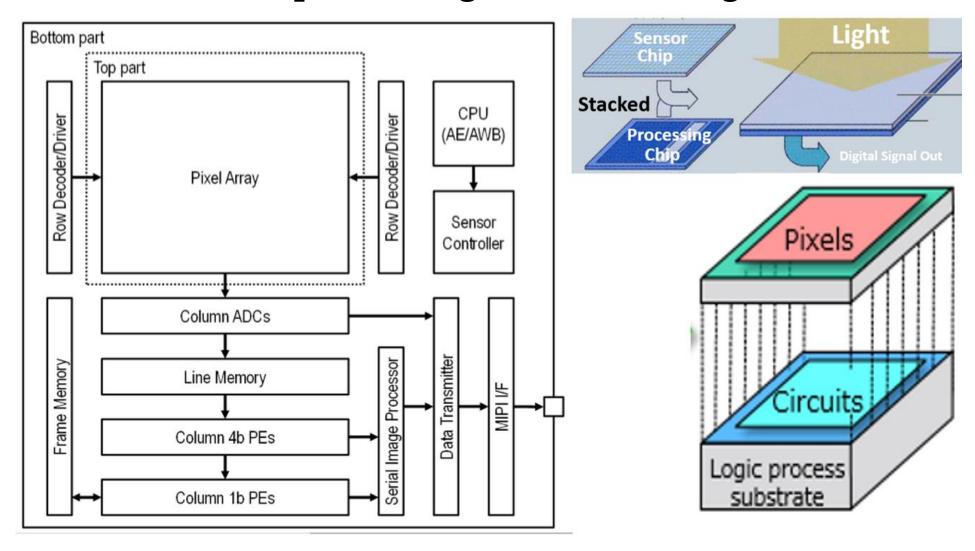

ISSCC 2017 / SESSION 4 / IMAGERS / 4.9

A 1ms High-Speed Vision Chip with 3D-Stacked 140GOPS Column-Parallel PEs for Spatio-Temporal Image Processing

Tomohiro Yamazaki¹, Hironobu Katayama¹, Shuji Uehara¹, Atsushi Nose¹, Masatsugu Kobayashi¹, Sayaka Shida¹, Masaki Odahara², Kenichi Takamiya², Yasuaki Hisamatsu², Shizunori Matsumoto², Leo Miyashita³, Yoshihiro Watanabe³, Takashi Izawa¹, Yoshinori Muramatsu¹, Masatoshi Ishikawa³

<sup>1</sup>Sony Semiconductor Solutions, Atsugi, Japan <sup>2</sup>Sony LSI Design, Atsugi, Japan <sup>3</sup>University of Tokyo, Bunkyo, Japan

High-speed vision systems that combine high-frame-rate imaging and highly parallel signal processing enable instantaneous visual feedback to rapidly control machines over human-visual-recognition speeds.

# 10 Multi Chip 3D Integration for Image Sensors and Solar Cells

3DIC2019.4017

2019 International 3D Systems Integration Conference (3DIC)

# Multichip CMOS Image Sensor Structure for Flash Image Acquisition

Yoshiaki Hagiwara

AIPS

Artificial Intelligent Partner Laboratory

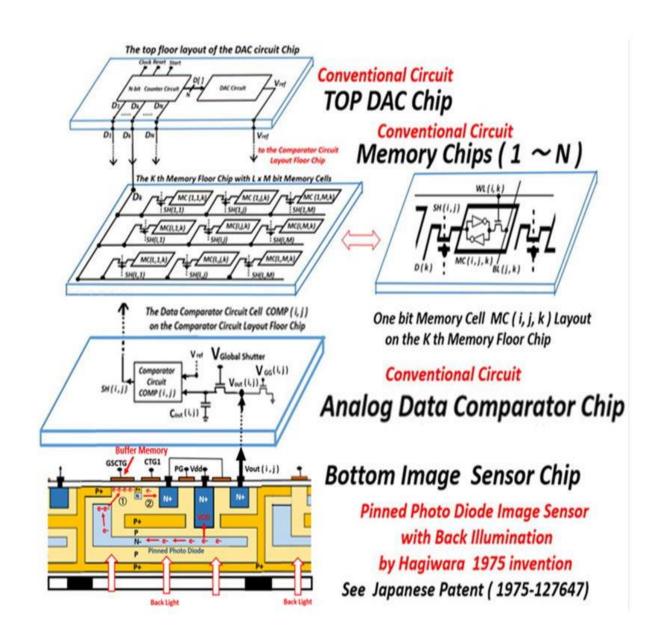

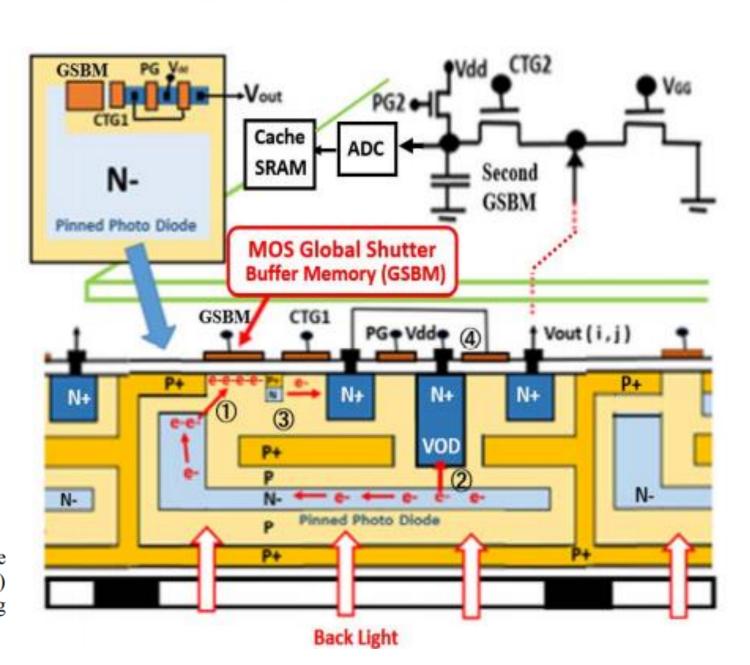

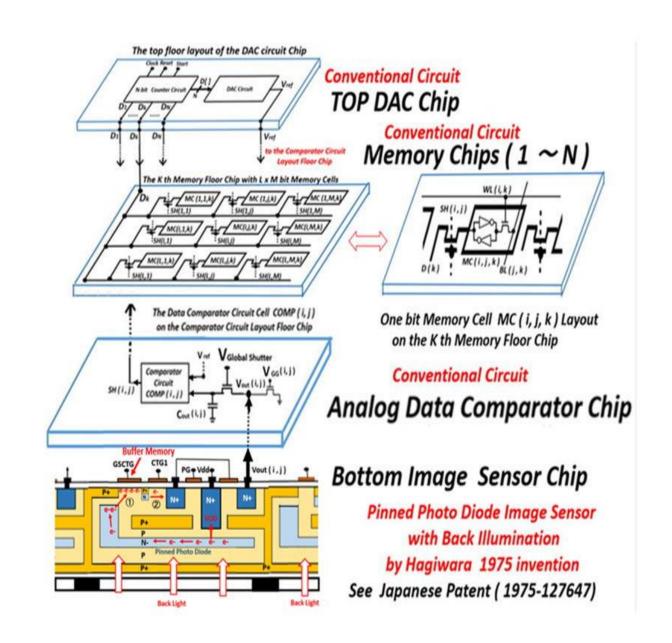

Abstract— A new 3D Pinned Photodiode (HAD) CMOS image sensor structure applied in the 3-Dimensional multichip high speed digital flash image data acquisition system is explained and the important features are discussed.

Keywords— Cache SRAM, ADC, Pinned Photodiode, Depletion Photodiode, Buried Photodiode, Back Light Illumination, Global Shutter Buffer Memory, In-pixel Three Transistor Current Source Amplifier.

# I. Introduction

Basically there are five types of photodiode. They are (1) Classic N+Psub junction with serious image lag problem (2) PNPsub junction Buried Photodiode (3) PN-Psub junction Depletion Photodiode with no image lag feature (4) P+N-P junction Pinned Photodiode with the heavily doped P+ surface hole accumulation with no surface dark current feature and (5) P+N-PNsub junction type hole accumulation diode (HAD) with the vertical overflow drain (VOD) function which is by necessity Buried, Depletion and Pinned Photodiode.

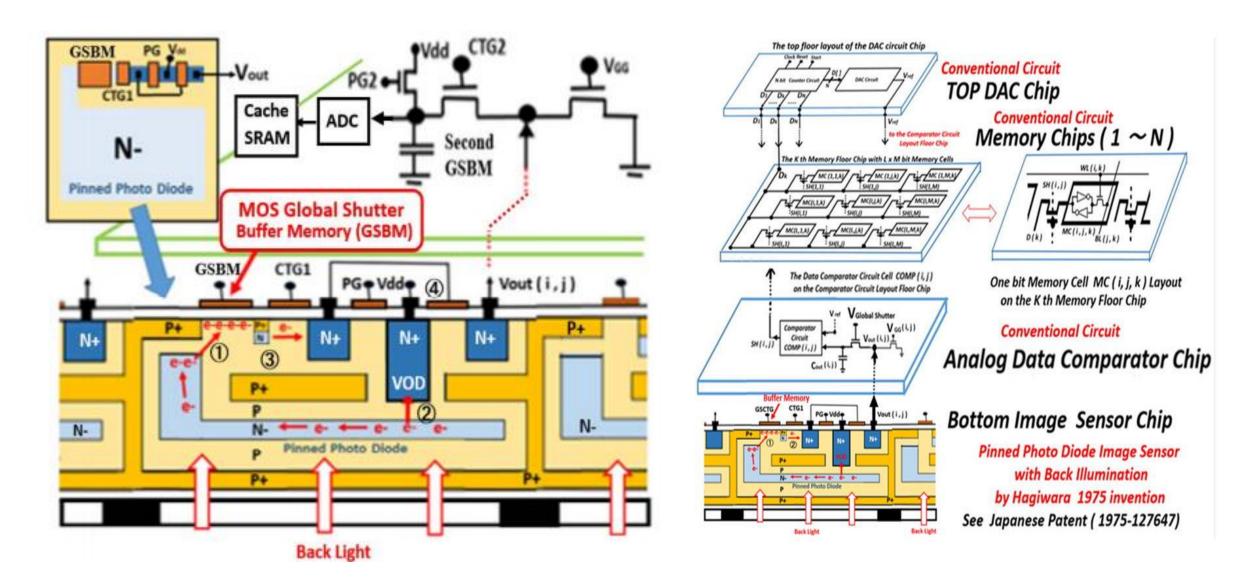

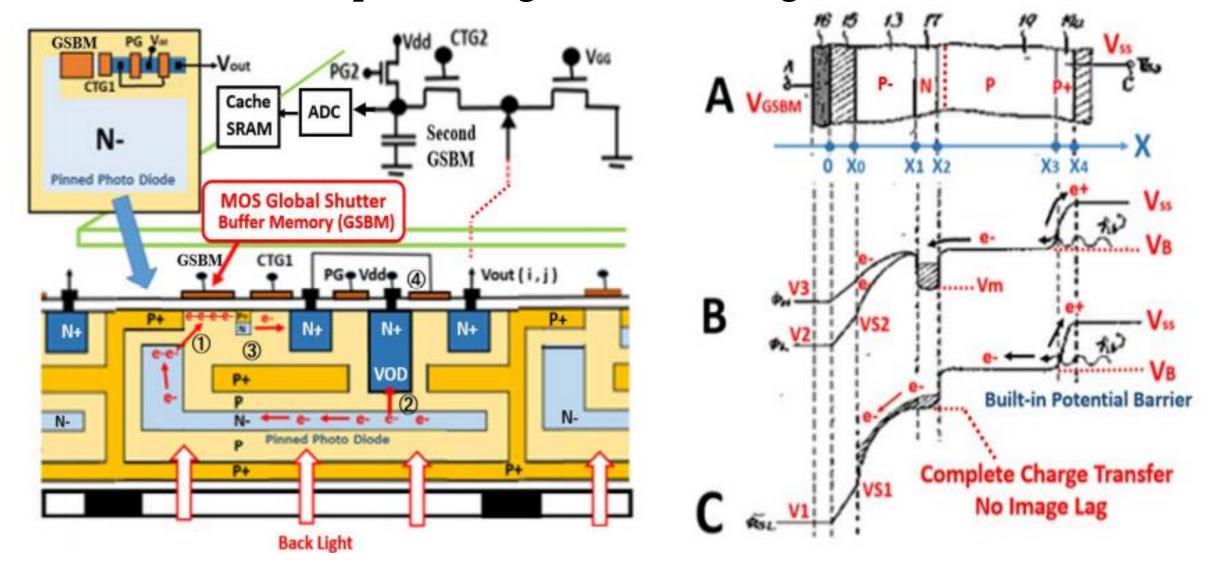

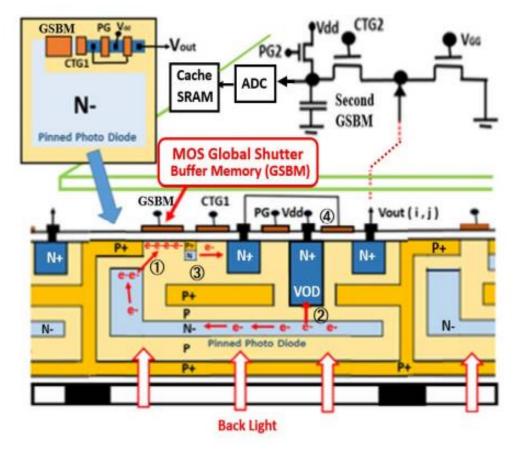

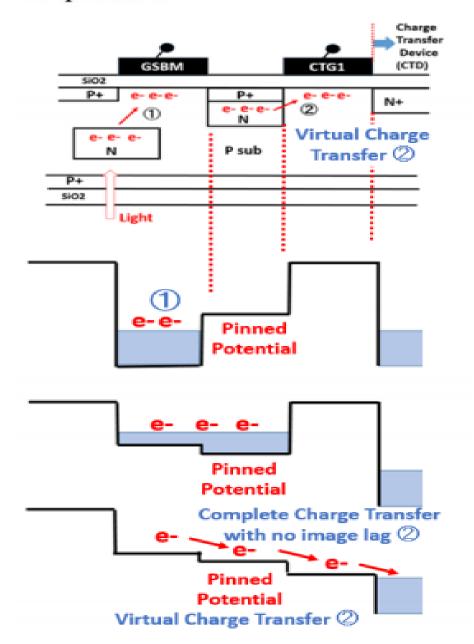

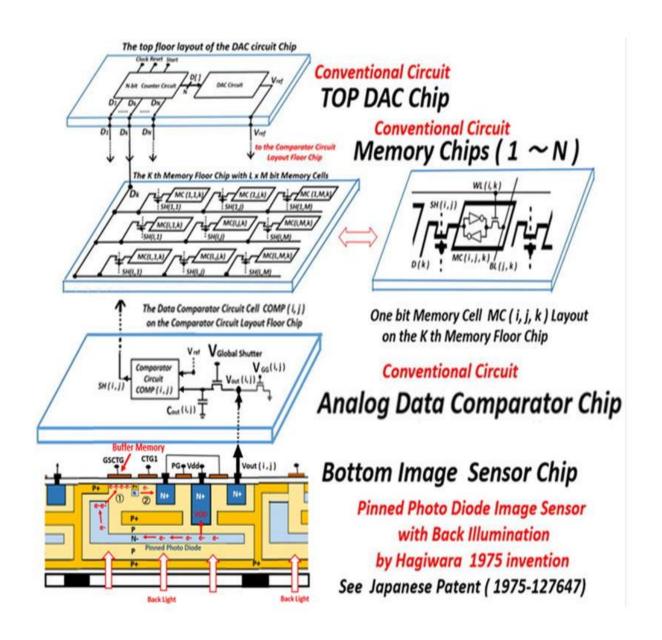

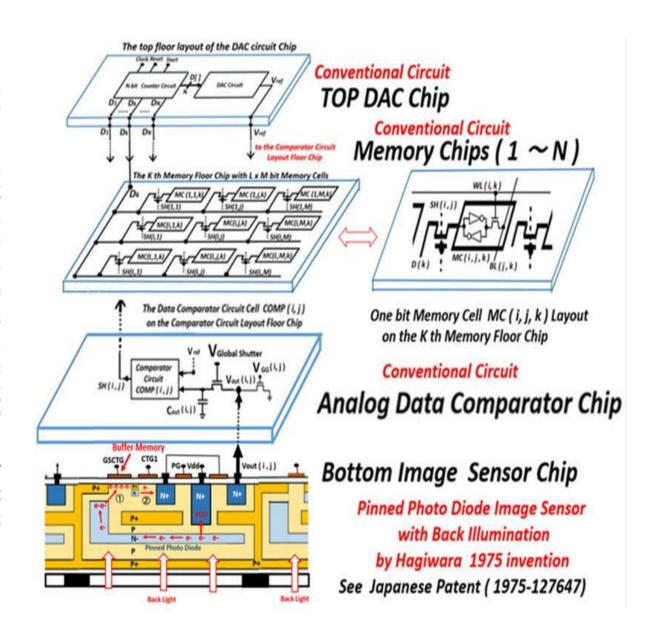

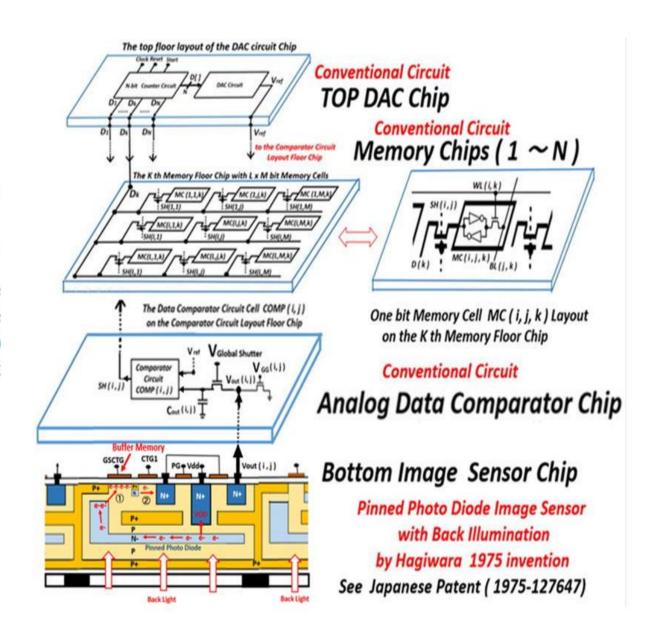

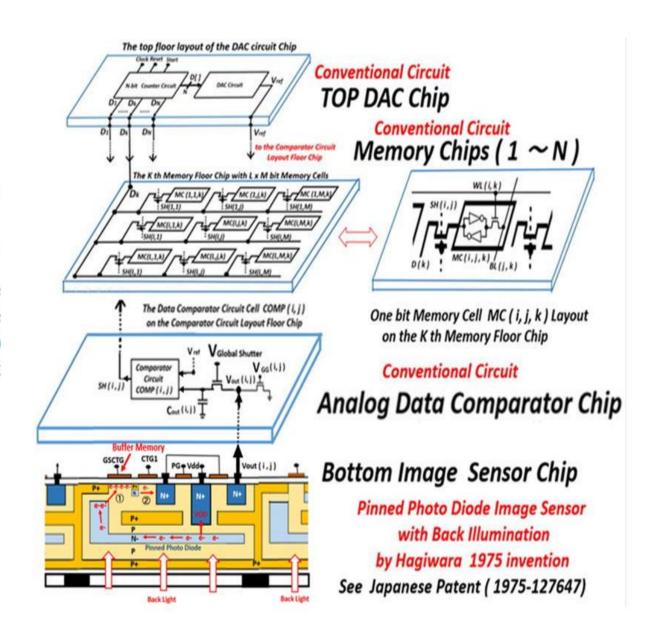

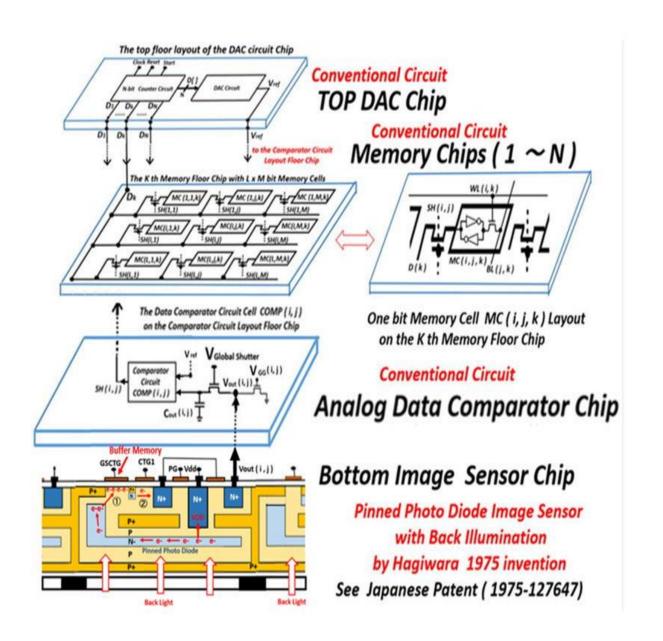

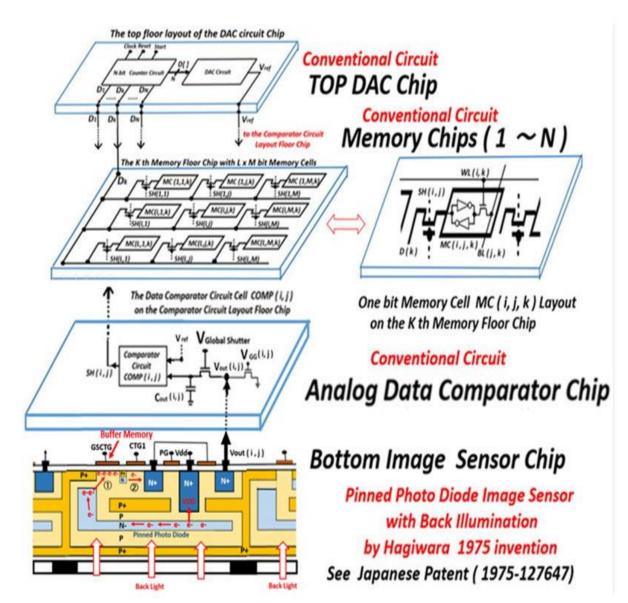

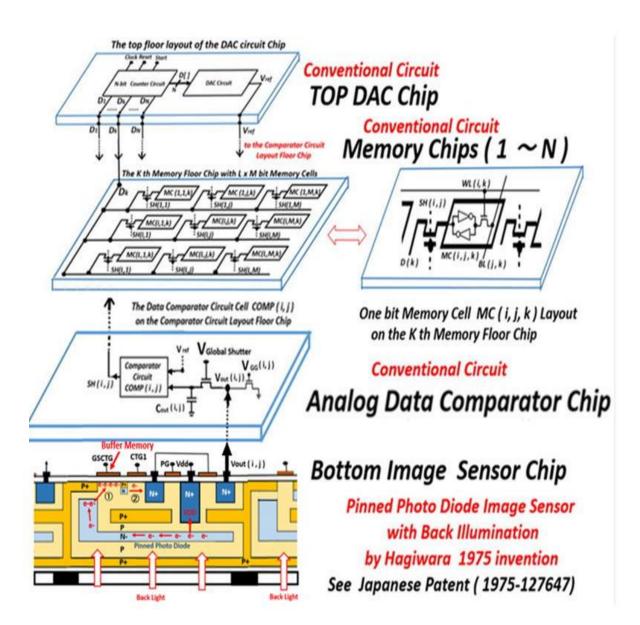

Photodiode. Fig. 1 shows the 3D multichip CMOS image sensor structure with the 3D Pinned Photodiode (HAD) image sensors with the MOS capacitor Global Shutter Buffer Memory (GSBM) which was originally invented in 1975.

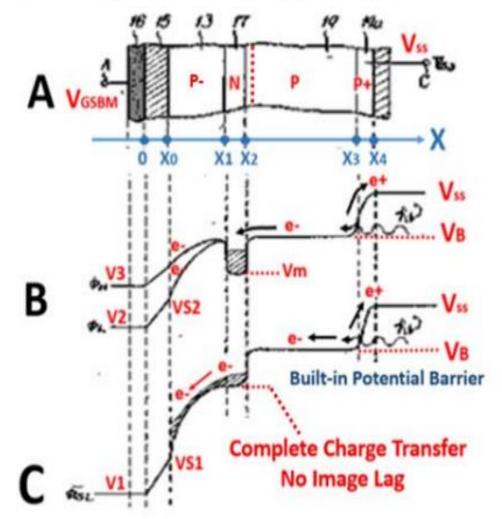

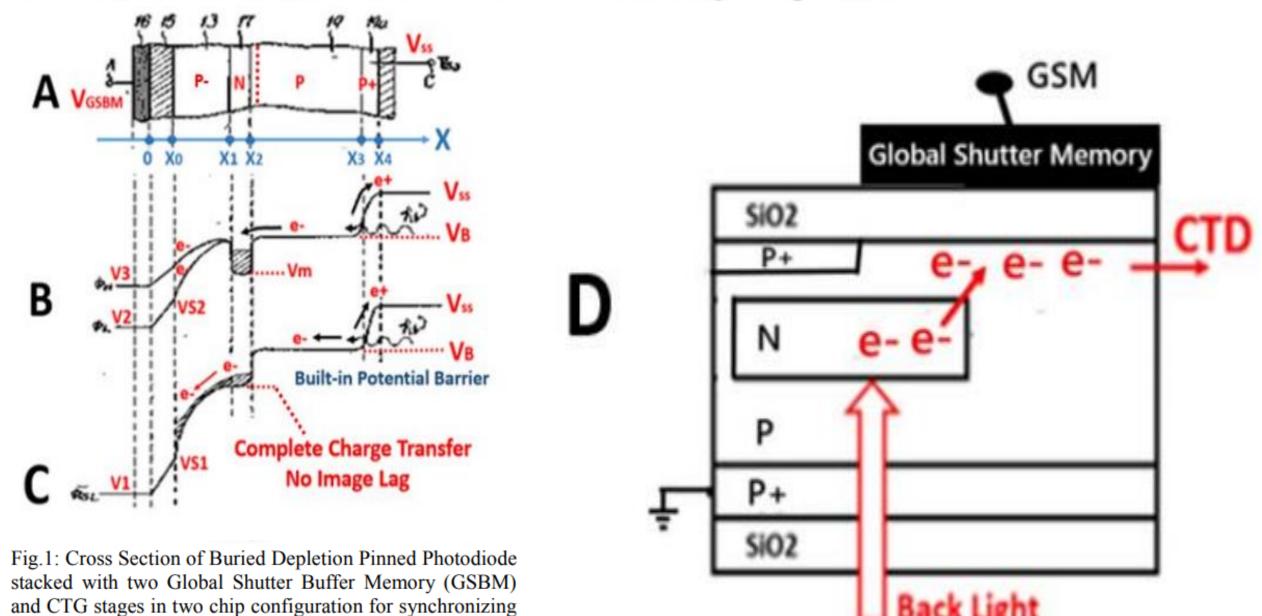

Fig.1: Cross Section of Buried Depletion Pinned Photodiode stacked with two Global Shutter Buffer Memory (GSBM) and CTG stages in two chip configuration for synchronizing data transfer to the receiving ADC and Cache SRAM chips.

Fig.1: Cross Section of Buried Depletion Pinned Photodiode stacked with two Global Shutter Buffer Memory (GSBM) and CTG stages in two chip configuration for synchronizing data transfer to the receiving ADC and Cache SRAM chips.

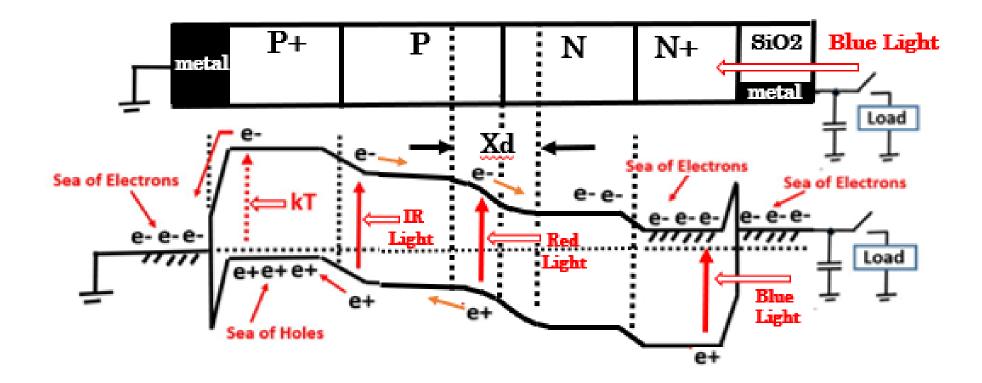

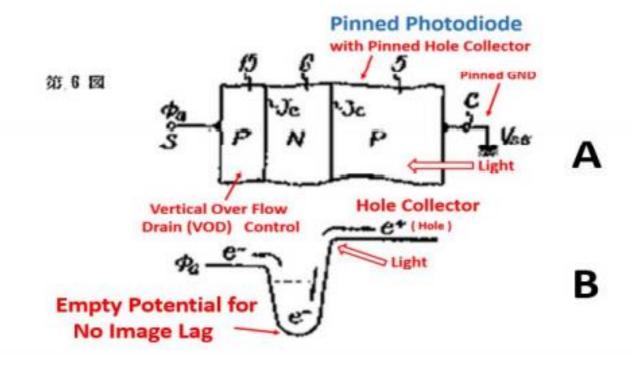

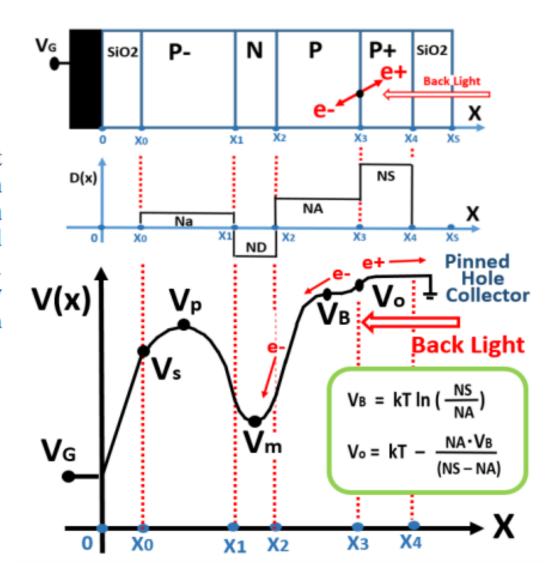

#### II. HOLE ROLE IN PINNED PHOTODIODE

The importance of holes in the hole accumulation layer HAD structure of Pinned Photodiode was first reported in Hagiwara 1978 paper<sup>2</sup>, and then explained in details by Theuwissen<sup>3</sup> in relationship with IDEM1982<sup>4</sup> paper and IEDM1984<sup>5</sup> paper. Today's success of super light sensitive digital imaging is based on the SiO2 exposed pinned window invented by Hagiwara in 1975<sup>1</sup> with the surface P+hole accumulation HAD layer. Pinned Photodiode was originally invented<sup>1</sup> in the form of the back illumination scheme as illustrated in Fig. 2.

data transfer to the receiving ADC and Cache SRAM chips.

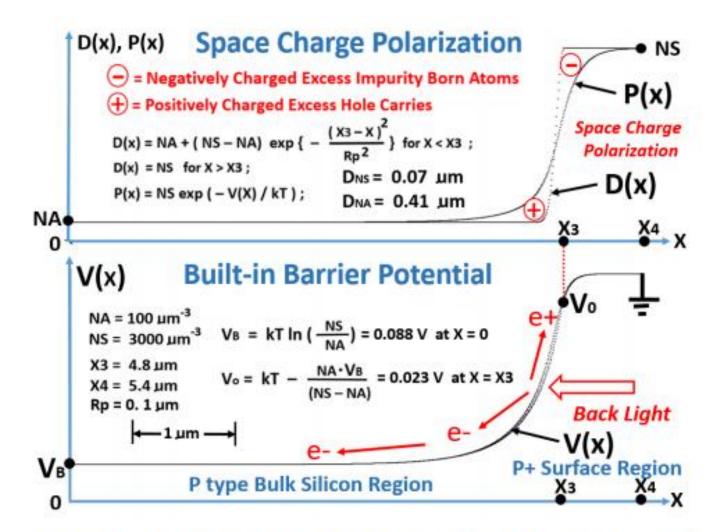

Fig. 3: Exact numerical calculations of Gaussian P+P doping profile D(x), the hole carrier density P(x) and the built-in barrier potential V(x).

#### III. ROLE OF BUILT-IN POTENTAIL BARRIER IN HAD

Exact numerical calculation of the built-in potential barrier is shown in Fig.3, explaining the hole electron generation and separation in the built-in electric field created by the heavily doped P+ surface hole accumulation HAD.

Note that the local unbalance of the hole concentration P(x) and the impurity boron atom density D(x) gives the local space charge polarization, resulting the built-in potential  $V_m$ . The built-in electric field separates photo electron hole pairs, and resulting in the excellent quantum efficiency of the short wave blue light sensitivity.

Although CCD was just a charge transfer device (CTD), later taken over by CMOS type CTD, both CCD and CMOS image sensors have the super sensitive light detecting feature with very good color reproduction at low light level because of the Pinned Photodiode which was invented and described in Japanese 1975 patent<sup>6</sup> by Hagiwara.

Fig. 3: Exact numerical calculations of Gaussian P+P doping profile D(x), the hole carrier density P(x) and the built-in barrier potential V(x).

In solar cells and image sensors, the photo electron and hole pair generation is considered to occur normally in the PN junction depletion region. However, the photo electron and hole pair generation in Pinned Photodiode is performed by an entire different physical principle. In 1975, Hagiwara proposed<sup>1</sup> that the photo electron and hole pair separation can also be achieved in the strong electric field created by the built-in barrier potential as shown in Fig. 2 that was the result of space charge polarization effect explained in Fig. 3.

Photo electrons are separated from holes in the presence of the surface built-in potential barrier near the border of the surface P+ hole accumulation HAD layer. And then, photo generated electrons can drift towards Buried Photodiode, which is the charge collecting storage, by using the holes, that is, positively charged Si ion atoms, as stepping stones, from one Si atom to another, like an energetic space rocket until it loses energy. If the photo electron, generated at the surface built-in potential barrier electric field, is recombined with a hole drifting deep in the bulk silicon, the hole becomes a neutral silicon atom that cannot move.

Photo electrons are separated from holes in the presence of the surface built-in potential barrier near the border of the surface P+ hole accumulation HAD layer. And then, photo generated electrons can drift towards Buried Photodiode, which is the charge collecting storage, by using the holes, that is, positively charged Si ion atoms, as stepping stones, from one Si atom to another, like an energetic space rocket until it loses energy.

If the photo electron, generated at the surface built-in potential barrier electric field, is recombined with a hole drifting deep in the bulk silicon, the hole becomes a neutral silicon atom that cannot move. Then, by the silicon bulk thermal neutrality condition, the excess negative space charge is present in the form of the trapped electron by the negatively charged boron or in the external orbit electron in the neutral Silicon atom at high energy state.

The electron has high energy state and can jump out into the free space. In this way, the excess negative charged electron cannot stay in the neutral silicon atom permanently and can be transferred to the positively charged silicon atom (hole) nearby, acting as stepping stones for the excess electron charge, eventually to drift towards the receiving Buried N type charge collecting region.

Eventually the excess electron negative charge is collected in the buried N type diffusion storage region. If the electric field of the PN junction depletion region edge of the buried photodiode is near the surface P+ hole accumulation edge, the drifting photo electrons can be quickly and instantly collected in the buried N type charge collecting storage area.

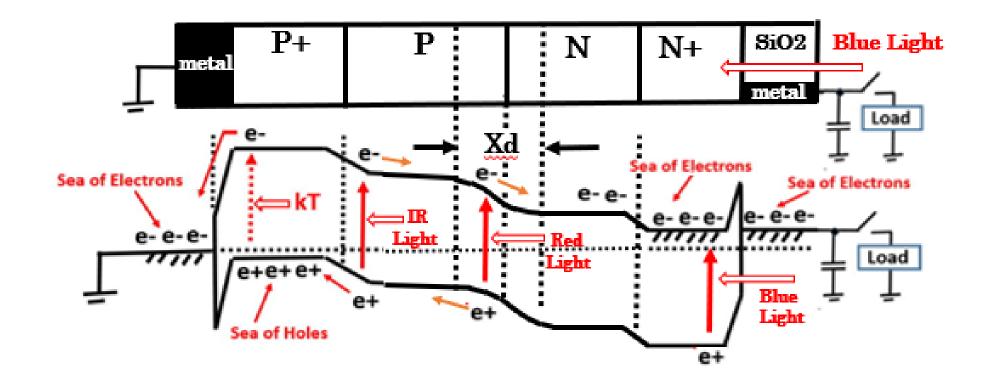

#### IV. VERTICAL OVERFLOW DRAIN (VOD) FUNCTION

Fig. 4 shows Pinned Photodiode with the vertical overflow drain (VOD), which is also Depletion Photodiode with no image lag feature. The following is the direct English translation of the Patent Claim of the Japanese 1975 patent<sup>6</sup> on Pinned Photodiode (HAD) invented by Hagiwara.

- In the substrate, the first region P1 of the first impurity type is formed, on which, the second region N2 of the second impurity type is formed.

- The charge e- from the light collecting part is transferred to the adjacent charge transfer device (CTD). Both are placed along the main surface of the semiconductor substrate.

- In the solid stare image sensor so defined, a rectifying junction Je is formed on the second light collecting region N2 forming the P3 and N2 junction as the emitter junction Je.

- 4. The result is a photo transistor P3N2P1structure on the substrate with the N2 and P1 junction as the collector junction Jc. The charge, stored in the base N2 region according to the illuminated light intensity, is transferred to the adjacent charge transfer device.

Fig. 4: The P+NPNsub junction type Hole Accumulation Diode (HAD)<sup>6</sup> invented by Hagiwara in 1975.

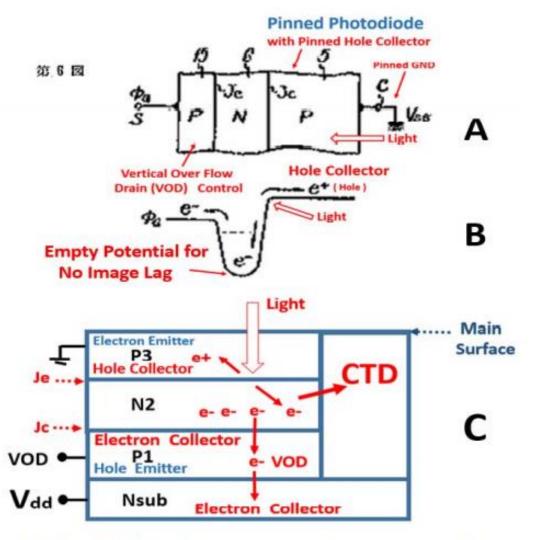

Fig. 5: Reproduction of figures reported in Hagiwara 1978 paper<sup>2</sup>, (A) P+NPsub junction type Pinned Photodiode structure, (B) the Excellent Blue Light Sensitivity (C) no dark current feature and (D) no image lag feature.

It is now well understood that the blue light of short wave length is needed for the satisfactory color reproduction of high image quality. However, the blue light cannot penetrate more than 0.3 micro meter in depth thru the silicon crystal<sup>7</sup>. The built-in surface potential barrier, created by the surface abrupt doping level difference, can in return create the strong electric field at the vicinity of the electron hole pair generation at the silicon surface of 0.3 micro meter in depth, which can effectively separate photo electron and hole pairs, resulting in the excellent quantum efficiency for the blue light needed for the satisfactory color reproduction.

#### IV. VERTICAL OVERFLOW DRAIN (VOD) FUNCTION

Fig. 4 shows Pinned Photodiode with the vertical overflow drain (VOD), which is also Depletion Photodiode with no image lag feature. The following is the direct English translation of the Patent Claim of the Japanese 1975 patent<sup>6</sup> on Pinned Photodiode (HAD) invented by Hagiwara.

- In the substrate, the first region P1 of the first impurity type is formed, on which, the second region N2 of the second impurity type is formed.

- The charge e- from the light collecting part is transferred to the adjacent charge transfer device (CTD). Both are placed along the main surface of the semiconductor substrate.

- In the solid stare image sensor so defined, a rectifying junction Je is formed on the second light collecting region N2 forming the P3 and N2 junction as the emitter junction Je.

- 4. The result is a photo transistor P3N2P1structure on the substrate with the N2 and P1 junction as the collector junction Jc. The charge, stored in the base N2 region according to the illuminated light intensity, is transferred to the adjacent charge transfer device.

P+NP junction type Pinned Photodiode(A) has the following three very important features, (B) Excellent short wave blue light quantum efficiency, which is the most important feature of Hagiwara 1975 patent<sup>6</sup>, (C) no surface dark current problem and (D) no image lag problem, with also the feature of no surface interface trap (Nss) noise (E). But nothing is new about the feature (D) and (E) since CCD had these two features already by 1975.

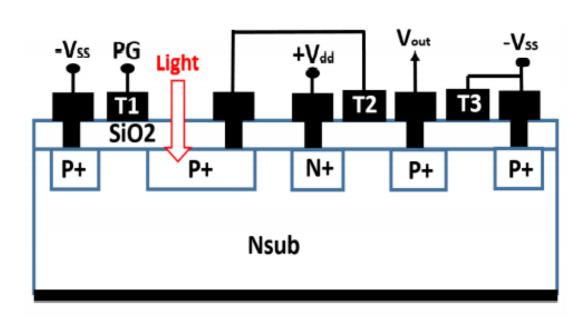

In 1966, the in-pixel active source follower amplifier circuit for MOS image sensors was invented by Perter Noble. See Fig. 6.

Fig. 6: In-pixel amplifier circuit by Peter Noble, 1966

But MOS scaling technology was not so advanced and the CCD type charge transfer device (CTD)<sup>8</sup> was preferred simply because MOS transistors were too large. However, CCD imager process shown in Fig. 4 was not as simple as MOS process for digital circuits. Complex bipolar transistor process experience was required. See Fig. 7. But now, owing to the advancement of CMOS process scaling, the active circuit of Fig. 6 became the most important element needed to build the modern CMOS image sensors<sup>9</sup>.

But MOS scaling technology was not so advanced and the CCD type charge transfer device (CTD)<sup>8</sup> was preferred simply because MOS transistors were too large. However, CCD imager process shown in Fig. 4 was not as simple as MOS process for digital circuits. Complex bipolar transistor process experience was required. See Fig. 7. But now, owing to the advancement of CMOS process scaling, the active circuit of Fig. 6 became the most important element needed to build the modern CMOS image sensors<sup>9</sup>.

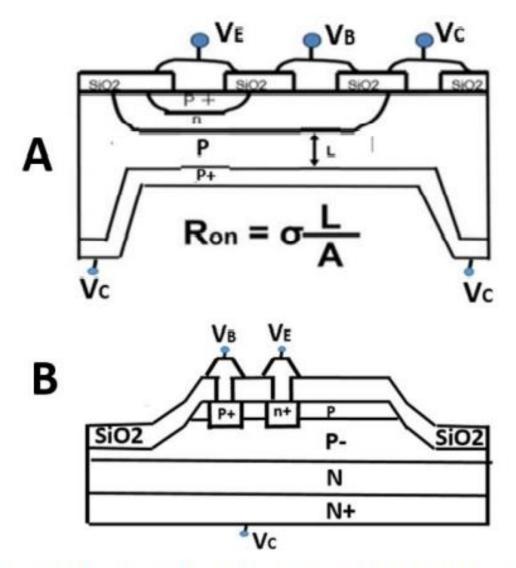

Fig. 7: Bipolar Transistor Process invented and developed by Yoshiyuki Kawana (A) and Toshio Kato (B) in 1950s.

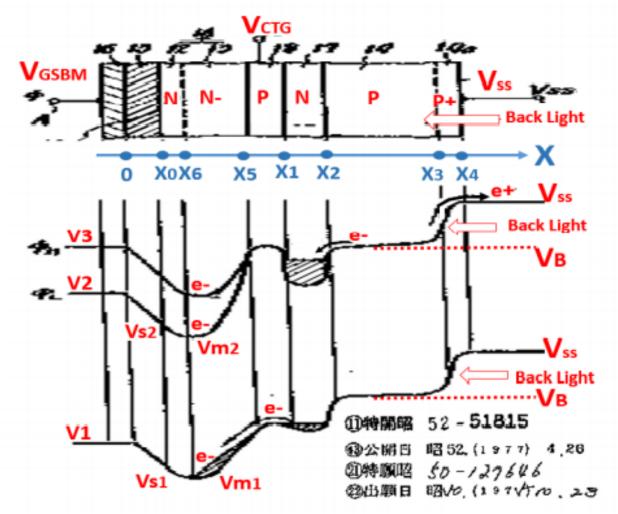

#### V. NPN JUNCTION CHARGE TRANSFER GATING (CTG)

Fig. 8 is a reproduction of the picture drawn in the 1975 patent<sup>10</sup> by Hagiwara. This charge transfer action is very similar to the well-known punch thru operation mode of the PNPN junction thyristor. Note that this is very similar to the P+NPN<sub>sub</sub> junction type Pinned Photodiode shown in Fig. 4. Both are the same PNPN junction type Pinned Photodiode.

Fig. 8: The P+PNPN junction type Pinned Photodiode<sup>10</sup> with Global Shutter MOS Buffer Memory (GSBM) and the NPN junction type vertical charge transfer gating (CTG).

#### VI. PINNED SURFACE VIRTUAL CHARGE TRANSFER

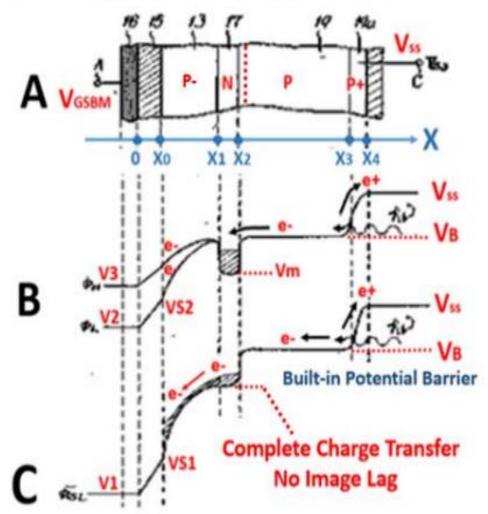

The charge transfer operation with the pinned surface potential for the virtual gating concept is very similar to the CCD charge transfer operation. Fig. 9 shows the virtual charge transfer concept explained by Hagiwara<sup>1,6,11</sup> in 1975. Henecek<sup>12</sup> invented an additional potential barrier stage to achieve the directionality of the virtual phase signal charge transfer operation, which was hinted by Hagiwara 1975 invention<sup>6</sup> and the virtual phase charge transfer operation of the image lag free Pinned Photodiode <sup>1</sup> as shown in Fig. 1.

Fig.9: The important concept of Virtual Phase Charge Transfer of the Pinned Photodiode with the complete charge transfer operation mode for no image lag feature, described and invented by Hagiwara 1975 patents<sup>1, 6, 10, 11</sup>.

VII. 3D MULTICHIP IMAGE SENSOR SYSTEM

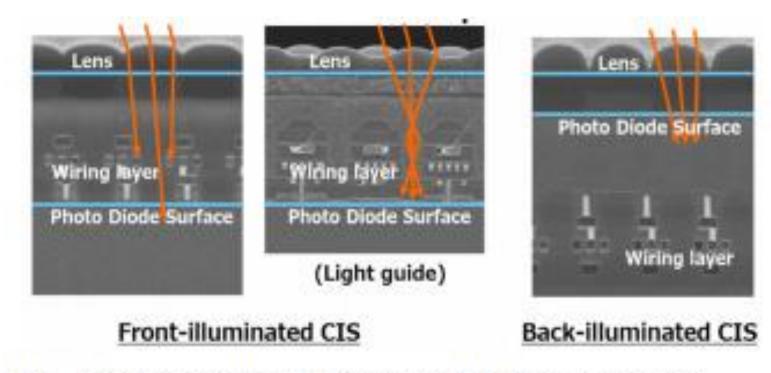

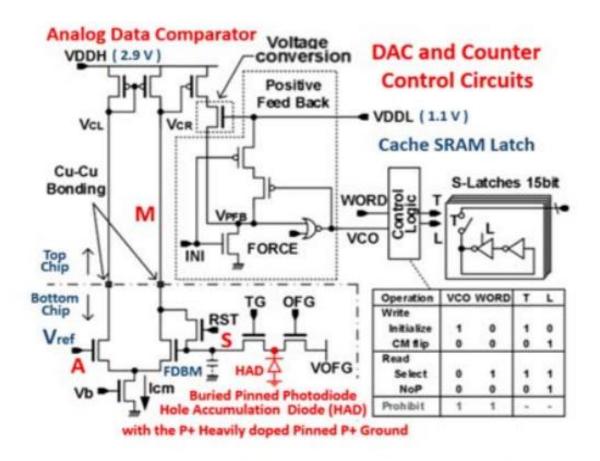

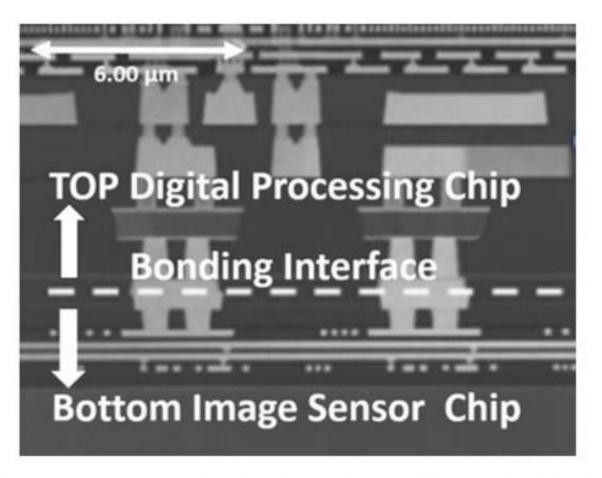

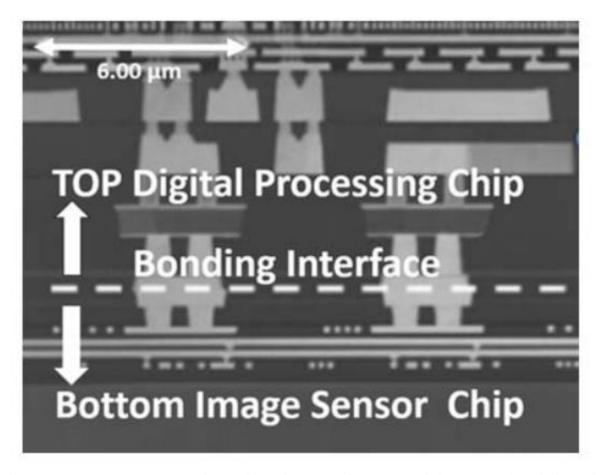

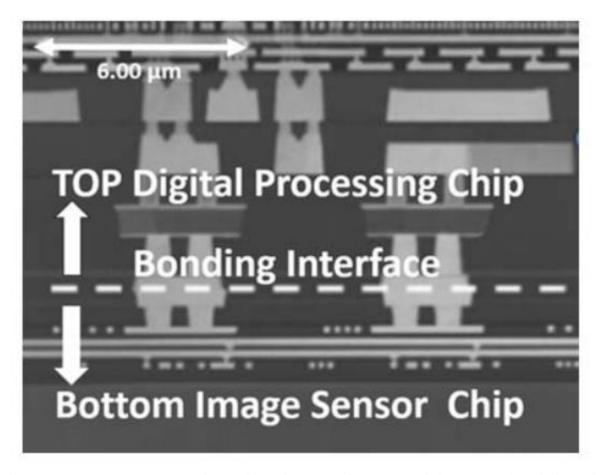

Cross sectional photos of back light illuminated CMOS image sensors are shown in Fig. 10 while Fig. 11 shows the 3D multichip CMOS image sensor system. If time sharing scheme is used, we only need one data comparator circuit.

However, for fast ADC operations, we must have the inpixel data comparator circuits that have to be squeezed in each pixel element area. The comparator circuit is a conventional one that can also be used for a simple IR sensor detector as shown in Fig. 12.

Fig. 10: Cross sectional photos of CMOS image sensors

#### VII 3D MULTICHIP IMAGE SENSOR SYSTEM

Cross sectional photos of back light illuminated CMOS image sensors are shown in Fig. 10 while Fig. 11 shows the 3D multichip CMOS image sensor system. If time sharing scheme is used, we only need one data comparator circuit.

However, for fast ADC operations, we must have the inpixel data comparator circuits that have to be squeezed in each pixel element area. The comparator circuit is a conventional one that can also be used for a simple IR sensor detector as shown in Fig. 12.

## Analog Data Comparator applied for IR Sensor VT must be equal to Vref. Rs (t) Vdd Rs (t) + RL Vin CdS Rs(t) Vout Vdd **IRsensor** Analog Data Comparator Circuit

##

Fig. 12: Conventional Analog Data Comparator Circuit

#### VIII. CIRCUIT SIMULATION OF ANALOG DATA COMPATOR

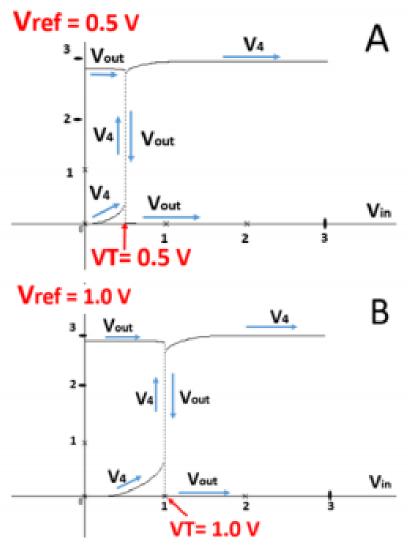

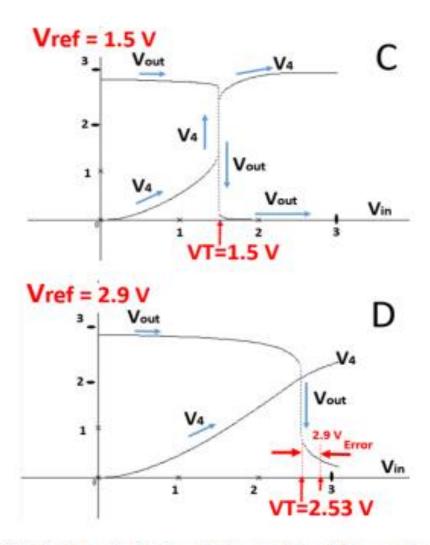

Fig.13 summarized the circuit simulation of the analog data comparator for the various reference voltage Vref values which correspond to the voltage A in Fig. 11. The input voltage Vin which corresponds to the output signal S in Fig.11 is scanned to obtain the value of the threshold voltage VT, which corresponds to the match signal M in Fig.11. With this match signal M, the cache SRAM latches the values of the control counter data D(1) to D(N) in each SRAM level chip. This simulation analysis shows the good circuit performance for the input reference voltage Vref at least in the range of 0 V to 1.5 V.

Fig.13: the circuit simulation results of the analog data comparator for the various reference voltage Vref values

#### VIII CIRCUIT SIMULATION OF ANALOG DATA COMPATOR

Fig.13 summarized the circuit simulation of the analog data comparator for the various reference voltage Vref values which correspond to the voltage A in Fig. 11. The input voltage Vin which corresponds to the output signal S in Fig.11 is scanned to obtain the value of the threshold voltage VT, which corresponds to the match signal M in Fig.11. With this match signal M, the cache SRAM latches the values of the control counter data D(1) to D(N) in each SRAM level chip. This simulation analysis shows the good circuit performance for the input reference voltage Vref at least in the range of 0 V to 1.5 V.

Fig.13: the circuit simulation results of the analog data comparator for the various reference voltage Vref values

#### IX ALL SOLID STATE DIGITAL CAMERA

The 25 nanosecond access time fast Cache 4 Mega Bit SRAM<sup>13</sup> was first developed in 1989, with the dynamic bit line load circuits invented by Miyaji, and was used as the very fast Digital Buffer Memory for the early all solid state digital CCD camera to correct and enhance the picture quality such as Jitter correction, color reproduction, pattern correction and image recognition processing system units for industrial and professional applications of high definition television broadcasting level.

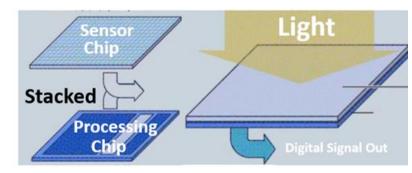

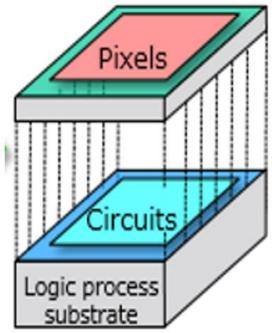

Fig. 14 shows the cross sectional view of two chip stacked back-illuminated CMOS image sensor 14-16 with the in-pixel analog comparator control circuits to generate the match signal M from the reference voltage A and the image sensor signal S, as originally illustrated in Fig. 11 for the future multichip system.

Fig. 14: Cross Sectional View of two chip stacked backilluminated CMOS Image Sensor<sup>14</sup> with the in-pixel analog comparator control circuits to generate the match signal M from the reference voltage A and the image sensor signal S.

#### IX ALL SOLID STATE DIGITAL CAMERA

The 25 nanosecond access time fast Cache 4 Mega Bit SRAM<sup>13</sup> was first developed in 1989, with the dynamic bit line load circuits invented by Miyaji, and was used as the very fast Digital Buffer Memory for the early all solid state digital CCD camera to correct and enhance the picture quality such as Jitter correction, color reproduction, pattern correction and image recognition processing system units for industrial and professional applications of high definition television broadcasting level.

Fig. 14 shows the cross sectional view of two chip stacked back-illuminated CMOS image sensor 14-16 with the in-pixel analog comparator control circuits to generate the match signal M from the reference voltage A and the image sensor signal S, as originally illustrated in Fig. 11 for the future multichip system.

Fig. 14: Cross Sectional View of two chip stacked backilluminated CMOS Image Sensor<sup>14</sup> with the in-pixel analog comparator control circuits to generate the match signal M from the reference voltage A and the image sensor signal S.

#### IX. ALL SOLID STATE DIGITAL CAMERA

The 25 nanosecond access time fast Cache 4 Mega Bit SRAM<sup>13</sup> was first developed in 1989, with the dynamic bit line load circuits invented by Miyaji, and was used as the very fast Digital Buffer Memory for the early all solid state digital CCD camera to correct and enhance the picture quality such as Jitter correction, color reproduction, pattern correction and image recognition processing system units for industrial and professional applications of high definition television broadcasting level.

Fig. 14 shows the cross sectional view of two chip stacked back-illuminated CMOS image sensor<sup>14-16</sup> with the in-pixel analog comparator control circuits to generate the match signal M from the reference voltage A and the image sensor signal S, as originally illustrated in Fig. 11 for the future multichip system.

Fig. 14: Cross Sectional View of two chip stacked backilluminated CMOS Image Sensor<sup>14</sup> with the in-pixel analog comparator control circuits to generate the match signal M from the reference voltage A and the image sensor signal S.

#### IX. ALL SOLID STATE DIGITAL CAMERA

The 25 nanosecond access time fast Cache 4 Mega Bit SRAM<sup>13</sup> was first developed in 1989, with the dynamic bit line load circuits invented by Miyaji, and was used as the very fast Digital Buffer Memory for the early all solid state digital CCD camera to correct and enhance the picture quality such as Jitter correction, color reproduction, pattern correction and image recognition processing system units for industrial and professional applications of high definition television broadcasting level.

Fig. 14 shows the cross sectional view of two chip stacked back-illuminated CMOS image sensor<sup>14-16</sup> with the in-pixel analog comparator control circuits to generate the match signal M from the reference voltage A and the image sensor signal S, as originally illustrated in Fig. 11 for the future multichip system.

Fig. 14: Cross Sectional View of two chip stacked backilluminated CMOS Image Sensor<sup>14</sup> with the in-pixel analog comparator control circuits to generate the match signal M from the reference voltage A and the image sensor signal S.

Photo electron and hole generation and separation at the surface electric field is performed at the back side silicon surface of the P+ heavily doped pinned hole accumulation (HAD) layer acting as the Pinned Hole Collector Grounded Terminal. Salient physical parameters are defined in Fig. 15. The all solid state CMOS image sensor technology is now being extended to the 3D multichip flash image acquisition system illustrated in Fig. 1 and Fig. 11.

Fig. 15: Electrostatic Analysis of the surface Built-in Barrier Potential V<sub>B</sub> and V<sub>o</sub> by Depletion Approximation.

#### X. CONCLUSION

Hole Accumulation Diode<sup>6</sup> (HAD), with the P+ heavily doped surface hole accumulation layer, invented in 1975, is very important, because first of all it has the excellent short wave length blue light sensitivity feature producing the high picture quality of color reproduction in low level light illumination, which is realized by the photo electron and hole pair generation and separation in the built-in potential barrier<sup>1</sup> and the electric field at the surface heavily doped P+ hole accumulation HAD. No dark current is the second important feature. And no image lag is the third one since CCD was known to have the no image lag feature already. But CCD itself does NOT have the excellent blue light sensitivity and does NOT have the low dark current feature which the Pinned Photodiode<sup>1,2,6,10</sup> invented by Hagiwara has.

HAD is defined as the PNPN junction Photodiode with the VOD function. HAD is also by necessity the P+N-P junction Pinned Photodiode with no dark current feature. HAD is also by necessity the PN-P junction Depletion Photodiode defined as Buried Photodiode with no image lag feature. When Hagiwara invented HAD<sup>1,2,6,10</sup> in 1975, Hagiwara also invented (1) Pinned Photodiode<sup>6</sup>, (2) Depletion Photodiode<sup>1</sup>, (3) Buried Photodiode<sup>10</sup>, (4) the inpixel vertical overflow drain<sup>6</sup> (VOD) function and (5) the in-pixel Global Shutter function<sup>1, 10</sup>. The surface pinned potential<sup>1, 6, 10</sup> also serves as the hole collector terminal separating the holes from photo electrons which drift more than the distance estimated by Debye length until being collected into the Buried<sup>10</sup>, Depletion<sup>1</sup> and Pinned<sup>6</sup> Photodiode (HAD), with the back light illumination scheme<sup>1</sup> which is the most important feature needed to build the super sensitive 3D CMOS image sensor with the high blue-light quantum efficiency and the excellent color reproduction at low light level for fast action pictures with no image lag.

Future AI traffic control system will need at least the high definition 8K image format of 7680H x 4320V, with 33 million pixels, to obtain the details of flash action images, with the in-pixel flash AD converters, and fast Cache SRAM chips in the 3D multichip CMOS image sensor with the more complex future digital circuit system implementations of the human friendly artificial intelligent partner system<sup>17</sup> (AIPS) to realize the smart AI image sensors for the smart AI robot vision system and home AI security and house cares..

Future AI traffic control system will need at least the high definition 8K image format of 7680H x 4320V, with 33 million pixels, to obtain the details of flash action images, with the in-pixel flash AD converters, and fast Cache SRAM chips in the 3D multichip CMOS image sensor with the more complex future digital circuit system implementations of the human friendly artificial intelligent partner system<sup>17</sup> (AIPS) to realize the smart AI image sensors for the smart AI robot vision system and home AI security and house cares..

## Acknowledgment

The author expresses sincere gratitude to Terushi Shimizu, Yasuhiro Ueda, Tadakuni Narabu, Junya Suzuki, Kato Toshio and Yoshiyuki Kawana, my dear friends and respectful mentors throughout private and public life at Sony.

- Japanese 1975-127647 Patent, filed on Oct 23, 1975 on Buried Deption and Pinned Photodiode with complete charge transfer and no image lag feature with MOS Capacitor type Global Shutter Buffer Memory (GSBM) function invented by Yoshiaki Hagiwara in 1975.

- [2] Y. Daimon-Hagiwara, M. Abe, and C. Okada, "A 380Hx488V CCD imager with narrow channel transfer gates, "Proc. of the 10th Conference on Solid State Devices, Tokyo, 1978; Japanese J. Appl. Phys., vol. 18, supplement 18–1, pp. 335–340.

- [3] Albert Theuwissen, "The Hole Role ", IEDM2005, IEDM Technical Digest, Dec 2005

- [4] N. Teranishi et.al., IEDM1982 Tech. Digest, pp. 324-32 on Buried Photodiode with no image lag. See also Japanese 1980-123259 patent filed in 1980, filed later than Japanese 1975-124985 patent in 1975.

- [5] B.C. Burkey et.al., IEDM Technical Digest, 1984, pp. 28-31 on Pinned Photodiode with the surface P+ hole accumulation layer, a dupicate device defined in the original Japanese 1975-124985 patent.

- [6] Japanese 1975-134985 Patent filed on Nov 10, 1975 on the P+NPNsub Buried Depletion and Pinned Photodiode with the surface P+ hole accumulation layer and the vertical overflow drain (VOD).

- [7] See Fig. 5, p.750, S. M. Sze, "Physics of Semiconductor Devices", 2nd Edition, Wiley.

- [8] K.Ishikawa and T.Iizuka, "One inch 2M pixel CCD with Hyper HAD sensor and Camera System for HDTV", SPIE proc. Vol. 1656, pp.30-40, February 1992.

- [9] K. Yonemoto and H. Sumi, "A CMOS Image Sensor with a Simple FPN Reduction Technology and a Hole Accumulation Diode", ISSCC2000, Digest of .Technical .Papers, pp.102-103, February 2000.

- [10] Japanese 1975-127646 Patent, filed on Oct 23, 1975 on the P+NPN junction type Buried, Depletion and Pinned Photodiode with the in-pixel MOS capacitor type buffer memory and the vertical NPN junction type charge transfer gating (CTG) for Global Shutter operation scheme.

- [11] Y. Hagiwara, "High-density and high-quality frame transfer CCD imager with very low smear, low dark current and very high blue sensitivity," IEEE Trans. Electron Devices, vol. 43, no. 12, pp. 2122–2130, Dec. 1996.

- [12] J. Hynecek, "Virtual phase CCD technology," in Proc. IEDM1979, pp. 611–614,Dec. 1979.

- [13] Fumio Miyaji, Yasushi Matsuyama, Yoshikazu Kanaishi, Katsunori Senoh, Takashi Emori and Yoshiaki Hagiwara, "A 25 nanosec 4 Mega bit CMOSRAM with Dynamic Bot-Line Loads", ISSCC1989 and J.Solid State Circuits, Vol24, No.5, October 1989.

- [14] M. Sakakibara, et al, "A Back-illuminated Global-Shutter CMOS Image Sensor with Pixel-Parallel 14b Subthreshold ADC", ISSCC2018, Feb. 2018

- [15] Y. Kumagai, et al, "Back-illuminated 2.74 um-Pixel-Pitch Global Shutter CMOS Image Sensor with Charge-Domain Memory Achieving 10k e- Saturation Signal "IEDM2018, Dec 2018.

- [16] Y. Kagawa and H. Iwamoto, "3D Integration Technologies for Stacked CMOS Image Sensors", an invited paper at the IEEE 3DIC2019 conference, Oct 8, 2019, Sendai, Japan

- [17] Yoshiaki IIagiwara, "The World of Digital Circuits for Artificial Intelligent Partner System (AIPS)", published by Seizansha.co.jp, in 2016, ISBN 978-4-88359-339-2, 450 pages, Hard Cover. 9000 yen+tax.